-

-

-

-

解决方案太原斯利德电子技术有限公司成立于1999年,是国内较早专门从事防信息泄漏(TEMPEST)、电磁兼容(EMC)技术研究的公司。产品已广泛用于航空、航天、船舶、陆用、安全保密工控等领域。

-

-

PCB中EMC设计的攻略宝典!

发布日期:

2023-02-13

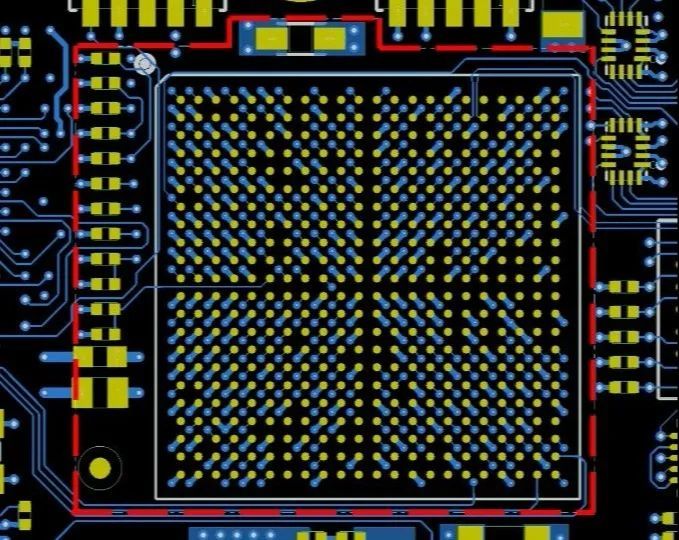

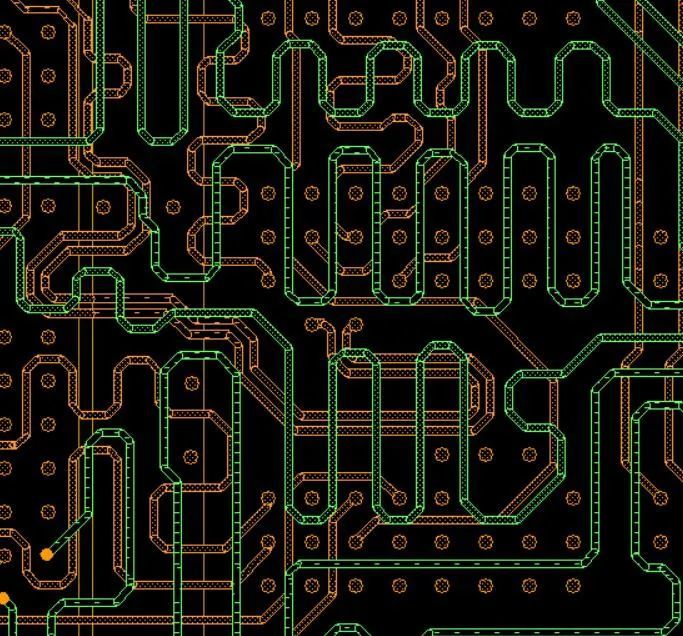

在PCB设计的过程中,从EMC角度,首先要考虑三个主要因素:输入/输出引脚的个数,器件密度和功耗。一个实用的规则是片状元件所占面积为基片的20%,每平方英寸耗散功率不大于2W。

一、器件的布局

在PCB设计的过程中,从EMC角度,首先要考虑三个主要因素:输入/输出引脚的个数,器件密度和功耗。一个实用的规则是片状元件所占面积为基片的20%,每平方英寸耗散功率不大于2W。

在器件布置方面,原则上应将相互有关的器件尽量靠近,将数字电路、模拟电路及电源电路分别放置,将高频电路与低频电路分开。

易产生噪声的器件、小电流电路、大电流电路等应尽量远离逻辑电路。对时钟电路和高频电路等主要干扰和辐射源应单独安排,远离敏感电路,输入输出芯片要位于接近混合电路封装的I/O出口处。

高频元器件尽可能缩短连线,以减少分布参数和相互间的电磁干扰,易受干扰元器件不能相互离得太近,输入输出尽量远离。震荡器尽可能靠近使用时钟芯片的位置,并远离信号接口和低电平信号芯片。

元器件要与基片的一边平行或垂直,尽可能使元器件平行排列,这样不仅会减小元器件之间的分布参数,也符合混合电路的制造工艺,易于生产。

在混合电路基片上电源和接地的引出焊盘应对称布置,最好均匀地分布许多电源和接地的I/O连接。裸芯片的贴装区连接到最负的电位平面。

在选用多层混合电路时,电路板的层间安排随着具体电路改变,但一般具有以下特征:

(1) 电源和地层分配在内层,可视为屏蔽层,可以很好地抑制电路板上固有的共模RF干扰,减小高频电源的分布阻抗。

(2) 板内电源平面和地平面尽量相互邻近,一般地平面在电源平面之上,这样可以利用层间电容作为电源的平滑电容,同时接地平面对电源平面分布的辐射电流起到屏蔽作用。

(3) 布线层应尽量安排与电源或地平面相邻以产生通量对消作用。

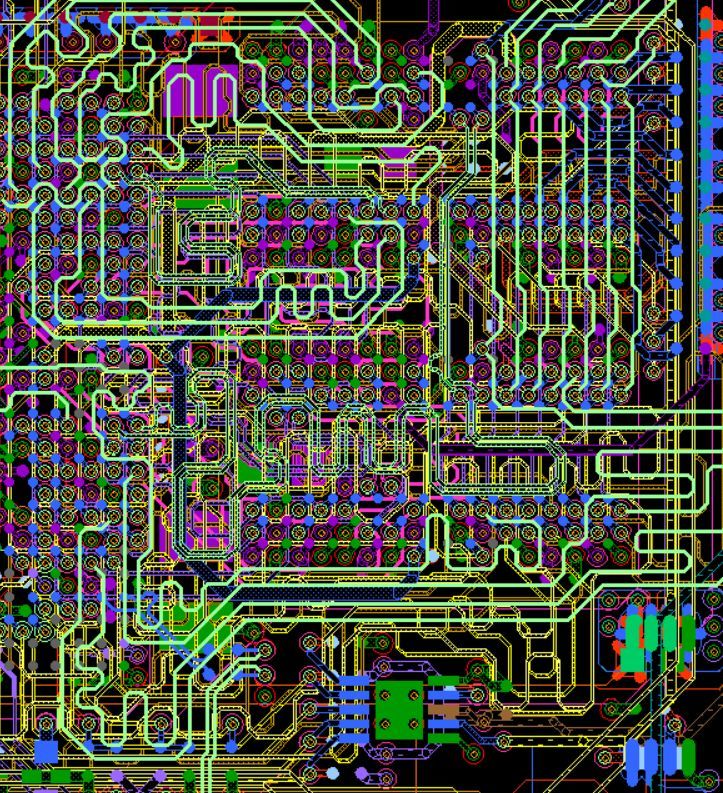

二、PCB走线

在电路设计中,往往只注重提高布线密度,或追求布局均匀,忽视了线路布局对预防干扰的影响,使大量的信号辐射到空间形成干扰,可能会导致更多的电磁兼容问题。

因此,良好的布线是决定设计成功的关键。

1、地线的布局

地线不仅是电路工作的电位参考点,还可以作为信号的低阻抗回路。

地线上较常见的干扰就是地环路电流导致的地环路干扰,解决好这一类干扰问题,就等于解决了大部分的电磁兼容问题。

地线上的噪音主要对数字电路的地电平造成影响,而数字电路输出低电平时,对地线的噪声更为敏感。

地线上的干扰不仅可能引起电路的误动作,还会造成传导和辐射发射。因此,减小这些干扰的重点就在于尽可能地减小地线的阻抗(对于数字电路,减小地线电感尤为重要)。

地线的布局要注意以下几点:

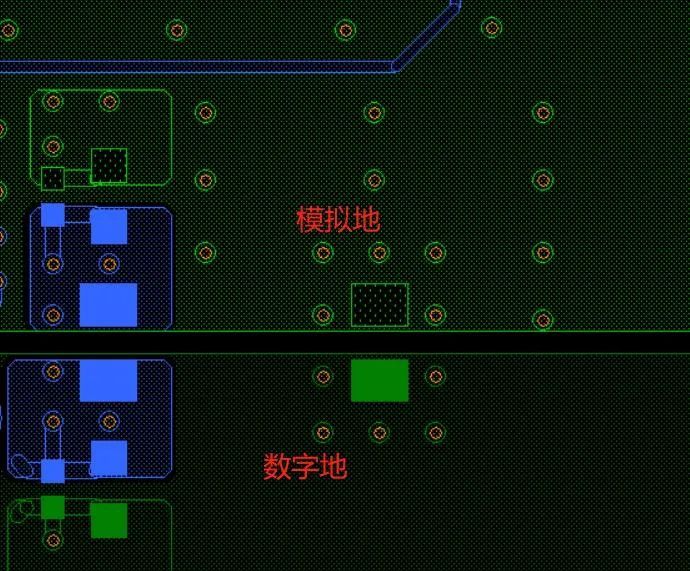

(1) 根据不同的电源电压,数字电路和模拟电路分别设置地线。

(2) 公共地线尽可能加粗。在采用多层厚膜工艺时,可专门设置地线面,这样有助于减小环路面积,同时也降低了接受天线的效率。并且可作为信号线的屏蔽体。

(3) 应避免梳状地线,这种结构使信号回流环路很大,会增加辐射和敏感度,并且芯片之间的公共阻抗也可能造成电路的误操作。

(4) 板上装有多个芯片时,地线上会出现较大的电位差,应把地线设计成封闭环路,提高电路的噪声容限。

(5) 同时具有模拟和数字功能的电路板,模拟地和数字地通常是分离的,只在电源处连接。

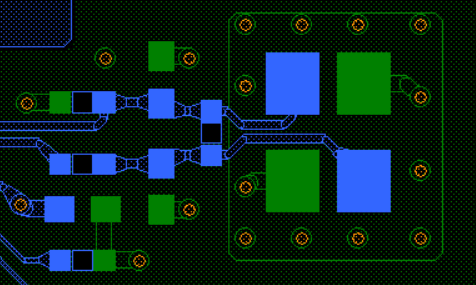

2、电源电路的布局

一般而言,除直接由电磁辐射引起的干扰外,经由电源线引起的电磁干扰最为常见。因此电源线的布局也很重要,通常应遵守以下规则。

(电源处理)

(1) 电源线尽可能靠近地线以减小供电环路面积,差模辐射小,有助于减小电路交扰。不同电源的供电环路不要相互重叠。

(2) 采用多层工艺时,模拟电源和数字电源分开,避免相互干扰。不要把数字电源与模拟电源重叠放置,否则就会产生耦合电容,破坏分离度。

(3) 电源平面与地平面可采用完全介质隔离,频率和速度很高时,应选用低介电常数的介质浆料。电源平面应靠近接地平面,并安排在接地平面之下,对电源平面分布的辐射电流起到屏蔽作用。

(4) 芯片的电源引脚和地线引脚之间应进行去耦。去耦电容采用0.01uF的片式电容,应贴近芯片安装,使去耦电容的回路面积尽可能减小。

(5) 选用贴片式芯片时,尽量选用电源引脚与地引脚靠得较近的芯片,可以进一步减小去耦电容的供电回路面积,有利于实现电磁兼容。

3、信号线的处理

在使用单层薄膜工艺时,一个简便适用的方法是先布好地线,然后将关键信号,如高速时钟信号或敏感电路靠近它们的地回路布置,最后对其它电路布线。

信号线的布置最好根据信号的流向顺序安排,使电路板上的信号走向流畅。

如果要把EMI减到最小,就让信号线尽量靠近与它构成的回流信号线,使回路面积尽可能小,以免发生辐射干扰。

低电平信号通道不能靠近高电平信号通道和无滤波的电源线,对噪声敏感的布线不要与大电流、高速开关线平行。如果可能,把所有关键走线都布置成带状线。不相容的信号线(数字与模拟、高速与低速、大电流与小电流、高电压与低电压等)

应相互远离,不要平行走线。

信号间的串扰对相邻平行走线的长度和走线间距极其敏感,所以尽量使高速信号线与其它平行信号线间距拉大且平行长度缩小。

导带的电感与其长度和长度的对数成正比,与其宽度的对数成反比。

因此,导带要尽可能短,同一元件的各条地址线或数据线尽可能保持长度一致,作为电路输入输出的导线尽量避免相邻平行,最好在之间加接地线,可有效抑制串扰。低速信号的布线密度可以相对大些,高速信号的布线密度应尽量小。

(相邻层尽量错开平行组线)

在多层厚膜工艺中,除了遵守单层布线的规则外还应注意:

尽量设计单独的地线面,信号层安排与地层相邻。不能使用时,必须在高频或敏感电路的邻近设置一根地线。

分布在不同层上的信号线走向应相互垂直,这样可以减少线间的电场和磁场耦合干扰;同一层上的信号线保持一定间距,最好用相应地线回路隔离,减少线间信号串扰。

每一条高速信号线要限制在同一层上。信号线不要离基片边缘太近,否则会引起特征阻抗变化,而且容易产生边缘场,增加向外的辐射。

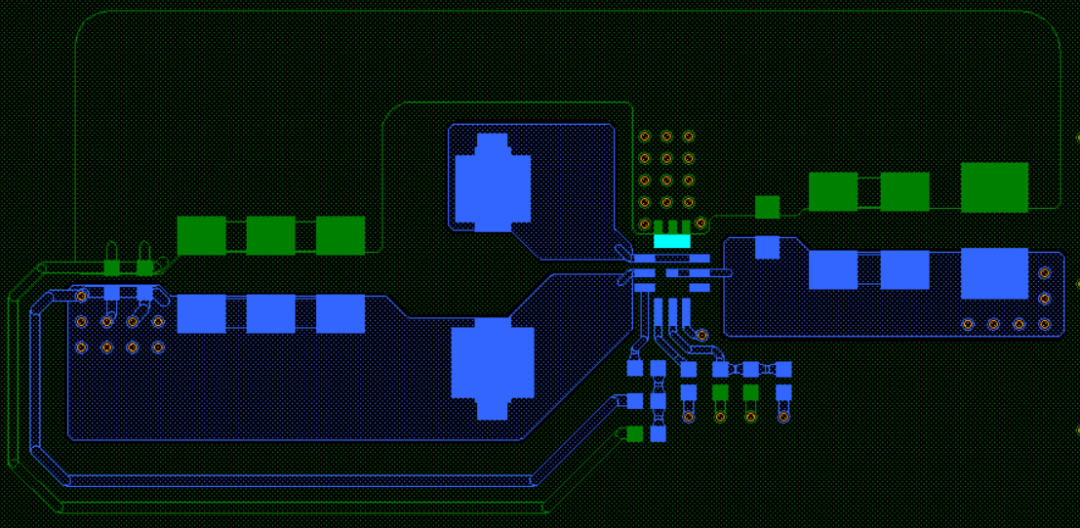

4、时钟电路处理

时钟电路在数字电路中占有重要地位,同时又是产生电磁辐射的主要来源。

一个具有2ns上升沿的时钟信号辐射能量的频谱可达160MHz。因此设计好时钟电路是保证达到整个电路电磁兼容的关键。

(时钟电路)

关于时钟电路的布局,有以下注意事项:

(1) 不要采用菊花链结构传送时钟信号,而应采用星型结构,即所有的时钟负载直接与时钟功率驱动器相互连接。

(2) 所有连接晶振输入/输出端的导带尽量短,以减少噪声干扰及分布电容对晶振的影响。

(3) 晶振电容地线应使用尽量宽而短的导带连接至器件上;离晶振最近的数字地引脚,应尽量减少过孔。

三、工艺和部件的选取

混合集成电路有三种制造工艺可供选择,单层薄膜、多层厚膜和多层共烧厚膜。

薄膜工艺能够生产高密度混合电路所需的小尺寸、低功率和高电流密度的元器件,具有高质量、稳定、可靠和灵活的特点,适合于高速高频和高封装密度的电路中,但只能做单层布线且成本较高。

多层厚膜工艺能够以较低的成本制造多层互连电路, 从电磁兼容的角度来说,多层布线可以减小线路板的电磁辐射并提高线路板的抗干扰能力。

因为可以设置专门的电源层和地层,使信号与地线之间的距离仅为层间距离。这样,板上所有信号的回路面积就可以降至最小,从而有效减小差模辐射。

其中多层共烧厚膜工艺具有更多的优点,是目前无源集成的主流技术。它可以实现更多层的布线,易于内埋元器件,提高组装密度,具有良好的高频特性和高速传输特性。

此外,与薄膜技术具有良好的兼容性,二者结合可实现更高组装密度和更好性能的混合多层电路。

混合电路中的有源器件一般选用裸芯片,没有裸芯片时可选用相应的封装好的芯片,为得到最好的EMC特性,尽量选用表贴式芯片。

选择芯片时在满足产品技术指标的前提下,尽量选用低速时钟。在HC能用时绝不使用AC,CMOS4000能行就不用HC。电容应具有低的等效串联电阻,这样可以避免对信号造成大的衰减。

混合电路的封装可采用可伐金属的底座和壳盖,平行缝焊,具有很好的屏蔽作用。

注:内容来自微信公众号“电磁兼容EMC”,如有侵权,请联系删除。

相关新闻

2024-04-09

2024-01-02